Kyrian BUNEL

Master ISC Systèmes électroniques année 2024 - 2025

Développement d’une carte horloge pour le projet ALMA

Rapport du stage au sein du laboratoire d'astrophysique de Bordeaux du 14/01/2025 au 27/03/2025

Tuteur de stage : M.Gauffre Stéphane - Ingénieur de recherche

Etablissement d'accueil : LAB - Bâtiment B18N, Allée Geoffroy Saint-Hilaire, 33600 PESSAC

Formation : Université de Bordeaux - Master Ingénierie des Systèmes Complexes

TABLE DES MATIÈRES

REMERCIEMENTS 2

INTRODUCTION 3

Contexte du stage 3

Présentation du laboratoire 3

Présentation du projet ALMA 5

Contexte et cahier des charges 7

Problématique 8

DÉVELOPPEMENT 8

Choix des composant de la carte d’alimentation DGCTR 8

Conception des étages de régulation 10

Conception des filtres 12

Simulation de la carte d'alimentation DGCTR 14

Conception d’une carte avec eCADstar 16

Importation des composants dans la bibliothèque 17

Création d’un composant (symbole, empreinte, propriétés) 17

Saisi du schéma 20

Routage de la carte 21

Conclusions 24

Annexes 25

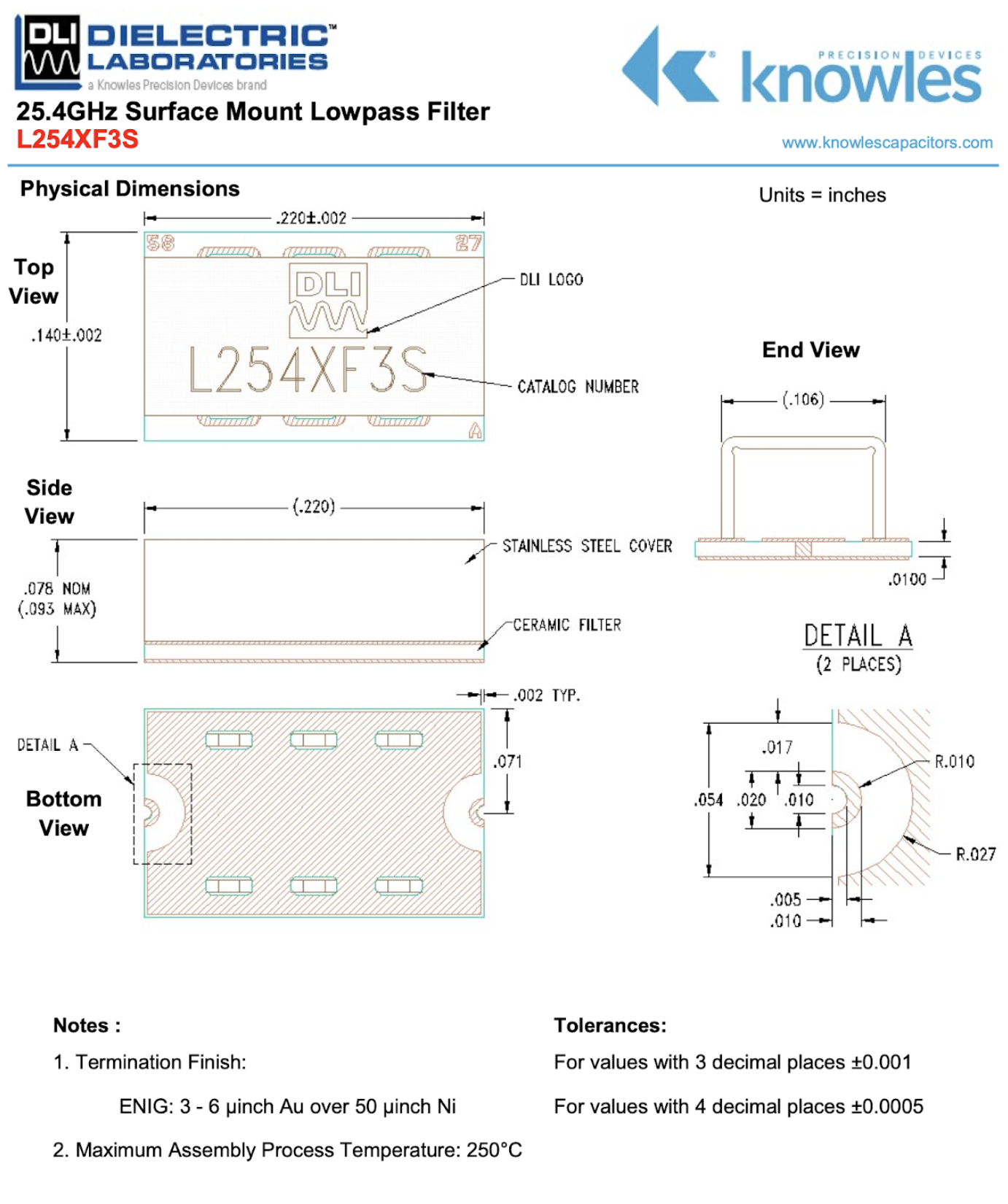

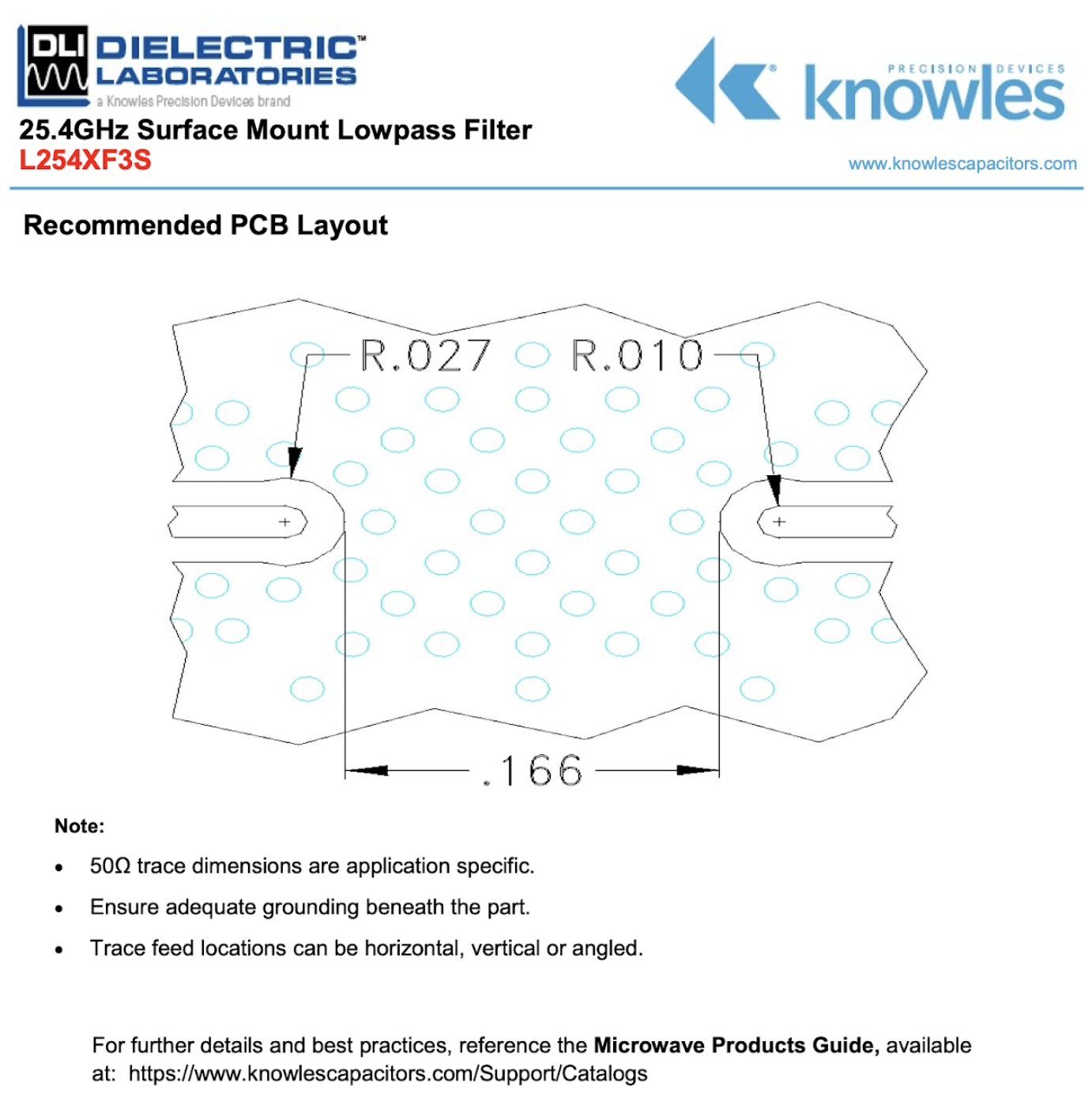

Annexe 1 : extrait de la Datasheet du L254XF3S montrant ses caractéristiques mécaniques et le layout recommandé par la fabricant 25

Annexe 2 : schémas réalisés de la carte DGCTR PLL 27

Annexe 3 : Rendu 3D final de la carte 28

REMERCIEMENTS

C’est avec la plus grande sincérité, que je tiens tout d’abord à remercier M. Stéphane GAUFFRE, mon maître de stage, qui exerce la fonction d’Ingénieur de recherche au sein du laboratoire d'astrophysique de Bordeaux, et qui m'a accueilli comme stagiaire au sein de l’équipe SEII (Système Electronique et Informatique Instrumental) du laboratoire LAB.

Au cours de mon stage, j’ai eu la chance de pouvoir bénéficier des conseils de l'ensemble des personnes de l'équipe électronique et je voudrais de même, les remercier pour le temps qu’ils m’ont accordé et leur aide précieuse.

Leur passion pour leur métier, leur implication dans le laboratoire, les valeurs qu’ils portent et leur souci de transmission, m'ont permis une intégration aisée et mon implication au quotidien. Ils m’ont beaucoup appris sur les enjeux de leur poste et sur leurs missions au quotidien.

Je souhaite également adresser mes remerciements les plus sincères aux équipes pédagogiques et administratives de l’université de Bordeaux qui ont facilité mes démarches et ont assuré un suivi tout au long de mon stage.

INTRODUCTION

Contexte du stage

J’ai découvert le laboratoire LAB à l’aide du réseau que j’ai pu me constituer l’année dernière lors de mon stage au laboratoire LP2I de Bordeaux.

Après des recherches nourries sur le laboratoire, j’ai tout de suite été attiré par les divers projets internationaux auxquels le laboratoire participe activement comme :

Systèmes de numérisation et de corrélation de l’interféromètre Atacama Large Millimeter Array (ALMA)

Instrument ChemCam à bord du rover martien Curiosity de l’agence spatiale américaine (NASA)

Instrument SuperCam à bord du rover martien Persévérance de la NASA

En totale adéquation avec mes attentes, j’ai donc postulé à l’offre de stage en envoyant mon CV ainsi qu’une lettre de motivation personnalisée à monsieur Stéphane Gaufre qui deviendra mon maître de stage.

A la suite d’un entretien physique avec une visite du bâtiment, j’ai eu l’opportunité de pouvoir intégrer l’équipe SEII du laboratoire le mardi 14 janvier 2025 en qualité de stagiaire.

Présentation du laboratoire

Le Laboratoire d'astrophysique de Bordeaux (LAB) est une unité mixte de recherche associant l'Université de Bordeaux et le Centre national de la recherche scientifique (CNRS). Il fait partie de l'Observatoire aquitain des sciences de l'Univers (OASU) et se consacre à trois missions principales :

La recherche fondamentale en sciences de l'Univers

La formation des étudiants par la recherche

La diffusion de la culture scientifique et technique

Les activités de recherche du LAB couvrent un large spectre, allant de l'étude du milieu interstellaire diffus à la formation des étoiles et des systèmes planétaires, en passant par les propriétés atmosphériques et de surface des planètes, jusqu'aux questions de climat, d'habitabilité et de recherche de la vie.

Le laboratoire est structuré en plusieurs équipes spécialisées :

- Astrochimie moléculaire et origine des systèmes planétaires (AMOR): Cette équipe se focalise sur l'astrochimie du milieu interstellaire et la physico-chimie des disques protoplanétaires.

- Atmosphères et surfaces planétaires (ASP): Elle étudie les atmosphères et les surfaces des planètes du Système solaire à travers l'analyse de données in situ ou de télédétection, ainsi que par la modélisation.

- Exoplanètes, climats et évolution des systèmes planétaires (ECLIPSE): Cette équipe aborde des questions liées à la formation et à l'évolution des systèmes planétaires, à la caractérisation des exoplanètes et à l'exobiologie.

- Formation d'étoiles et milieu interstellaire (FEMIS): Elle se consacre à la formation stellaire et à la structure du milieu interstellaire.

- Métrologie de l'espace, astrodynamique, astrophysique (M2A): Cette équipe contribue à des avancées majeures dans les systèmes de référence fondamentaux aux échelles galactiques et extragalactiques, en astrométrie et en caractérisation de populations stellaires.

- SEII: L'équipe SEII du LAB possède un savoir-faire unique en électronique pour la radioastronomie et le pilotage d'instruments embarqués sur des sondes spatiales. Elle développe des systèmes électroniques avancés pour des projets d'observation au sol et des missions spatiales, contribuant ainsi à l'innovation technologique dans le domaine de l'astrophysique.

- Mécanique: Cette équipe offre un potentiel de fabrication mécanique de précision pour l'instrumentation au sol et dans l'espace.

Le LAB dispose également d'un Service Administration, Finances, Infrastructure et Ressources Humaines (SAFIRH) qui assiste la direction et accompagne les équipes scientifiques et techniques dans la réalisation de leurs projets.

Installé depuis juillet 2016 dans le bâtiment B18N du campus universitaire de l'Université de Bordeaux à Pessac, le LAB continue de jouer un rôle central dans l'avancement des connaissances en astrophysique.

Présentation du projet ALMA

Le projet ALMA (Atacama Large Millimeter/submillimeter Array) est un réseau de 66 antennes paraboliques installé à 5000 mètres d’altitude dans le désert d’Atacama, au Chili. Il est conçu pour observer les longueurs d’onde millimétriques et submillimétriques, permettant l’étude des protoétoiles, des disques protoplanétaires, des galaxies lointaines et du milieu interstellaire.

figure 1 : Antennes sur le site ALMA (5000m)

L’astronomie millimétrique permet d’observer des structures froides et peu lumineuses, invisibles aux instruments optiques ou infrarouges. Cependant, ces ondes sont fortement atténuées par la vapeur d’eau atmosphérique, d’où l’implantation en altitude.

Un autre défi majeur est la résolution des images, pour obtenir une finesse équivalente à celle d’un télescope de plusieurs kilomètres de diamètre, ALMA utilise l’interférométrie, combinant les signaux de ses antennes avec une précision temporelle de l’ordre de la picoseconde. Cela nécessite une architecture électronique avancée, capable de synchroniser, numériser et traiter ces signaux avec une grande rapidité et stabilité.

L’électronique d’ALMA est conçue pour capter, traiter et synchroniser les signaux astronomiques avec une précision extrême. Elle est organisée en plusieurs sous-systèmes :

Récepteurs cryogéniques (Front-End)

Chaque antenne est équipée de récepteurs refroidis à 4 kelvin, sensibles aux bandes millimétriques et submillimétriques (de 31 GHz à 950 GHz). Ces récepteurs amplifient les signaux extrêmement faibles provenant de l’espace avant leur traitement.

Système de conversion de fréquence (Back-End)

Convertit les signaux haute fréquence vers des bandes plus basses adaptées au traitement électronique.

Ce système de conversion de fréquence doit être remplacé à horizon 2030 par un système de conversion analogique-numérique direct à 40 Géchantillons par seconde afin de doubler la bande d’analyse de l’instrument ALMA (8 GHz aujourd’hui, 16 GHz en 2030).

L’utilisation de convertisseurs analogique-numérique (ADC) à haute vitesse (40 Gech/s) pour permettre la numérisation des signaux radio de largeur de bande 16 GHz pour ensuite transmettre les données via un réseau de fibres optiques haute performance (4 x 400 Gbps par antenne), reliant chaque antenne au super calculateur (corrélateur ALMA).

Le module DGCTR (Digitizer Clock and Time Reference) est un élément clé du nouveau système électronique, assurant la génération de l’horloge d’échantillonnage à 20 GHz et la resynchronisation du signal de référence « TE ». Ses principales fonctions sont décrites par le schéma, ci-après :

figure 2 : schéma de la partie radiofréquence de la carte DGCTR

Un circuit à boucle à verrouillage de phase (PLL : Phase Locked Loop) pour la génération, à partir d’une horloge de référence à 125 MHz, de l’horloge d’échantillonnage à 20 GHz, qui sera utilisé par les ADC à 40 Géch/s pour la numérisation du signal radio. Ces ADC ayant une topologie deux cœurs entrelacés qui effectue un échantillonnage sur les fronts montants et les fronts descendants de l’horloge à 20 GHz, permettent d’obtenir un échantillonnage équivalent à 40 GHz.

Un circuit de synchronisation sur l’horloge de référence à 125 MHz, du signal de référence, appelé TE (Time Event). Ce signal de référence sera numérisé par les ADC afin de réaliser :

Un « alignement » des récepteurs des circuits logiques programmables (FPGA) utilisés pour la capture des échantillons numériques provenant des ADC.

Une datation des échantillons numériques,

ALMA est un projet de pointe en radioastronomie, nécessitant une électronique ultra-performante pour assurer la précision et la fiabilité des observations. La carte DGCTR joue un rôle clé dans la synchronisation et le traitement des données numériques, garantissant la cohérence des observations interférométriques. Son architecture repose sur des modules avancés, qui permettent d’aligner les antennes avec une précision inégalée.

Contexte et cahier des charges

Ma première mission durant ses trois mois de stage est de concevoir la partie alimentation de la carte DGCTR afin de fournir les tensions nécessaires au bon fonctionnement de la carte. L’objectif est de générer plusieurs niveaux de tensions, 8.5V, -3.8V, 6.5V, 5V, 3.8V et 3.3V (PLL) à partir d’une tension d’alimentation de +24V en entrée.

Ma seconde mission est de réaliser le schéma de la partie haute fréquence comportant plusieurs composants sensibles comme une PLL, des filtres passe-bas et passe-bandes ainsi que des amplificateurs haute fréquence pouvant monter jusqu’à 20GHz imposant ainsi des contraintes de design.

La conception de la carte est soumise à plusieurs contraintes :

La première est le milieu dans lequel la carte DGCTR va opérer. En effet, étant donné que celle-ci se trouve en altitude, son refroidissement est limité, il faut donc surdimensionner les composants et les circuits intégrés afin de garantir une durée de vie de la carte de plus de 15 ans. Pour se faire, lors du choix des composants un facteur 2 sera appliqué.

La seconde contrainte vient de la nature des composants à alimenter et des signaux RF. En effet, les composants à alimenter fonctionnent à haute fréquence ; la stabilité de l’alimentation est alors cruciale pour ce type d’applications tout en communiquant le moins de bruit possible. Il est donc primordial de sélectionner des composants à faible bruit (silencieux) et de mettre en place des filtres afin de fournir des tensions d’alimentation les plus propres possible.

Problématique

Dans ce rapport, nous allons voir au travers de mon expérience acquise, durant ses 3 mois de stage, au sein du LAB, quelles sont les étapes de conception d’une carte électronique en accord avec les normes IPC (normes utilisées pour la conception, la fabrication et l’assemblage des cartes électroniques) ?

DÉVELOPPEMENT

Choix des composant de la carte d’alimentation DGCTR

La première étape de conception est de sélectionner les composants nécessaires tout en se conformant au cahier des charges imposé.

Pour ce faire, j'utilise donc les outils en ligne d’Analog Devices, concepteur de circuits intégrés et développeur du logiciel de simulation LTspice afin de choisir les circuits intégrés que je vais par la suite utiliser.

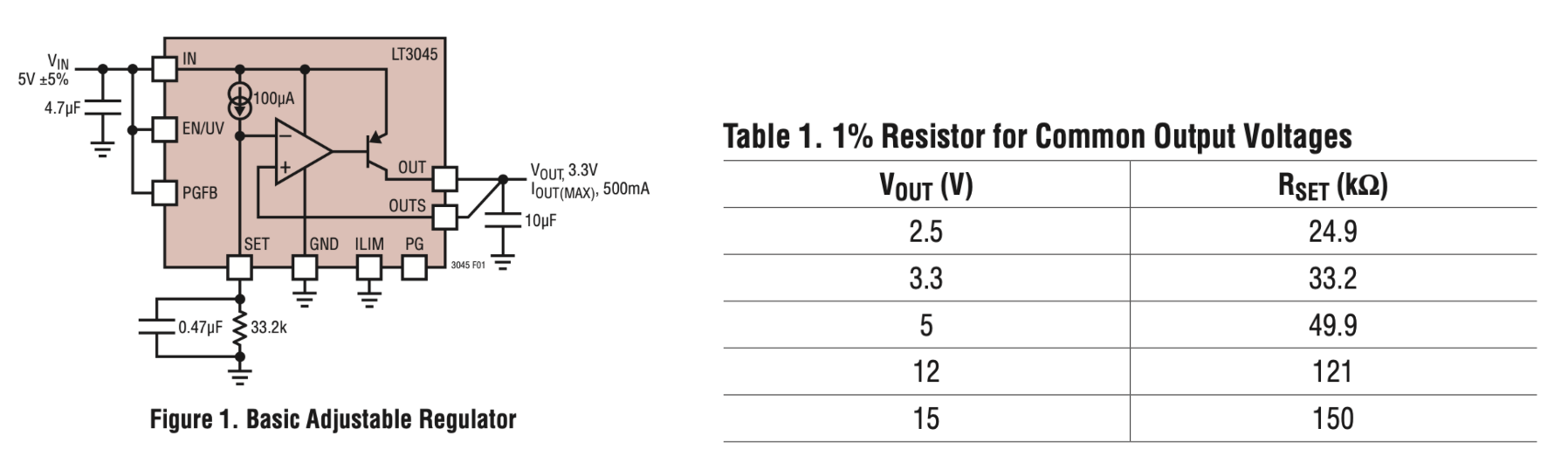

Afin de sélectionner le régulateur qui correspond au mieux à mon cahier des charges, parmi près de 2000 références, j’utilise les filtres de recherche du site d’analog devices et détermine les critères suivants :

un convertisseur DC/DC : abaisseur de tension

recommandé pour les nouvelles conceptions : indique que le cycle de vie du composant n’est qu'à son début et assure une bonne disponibilité dans le temps de la carte du composant tout au long des phases du projet : développement, production , maintenance

doté d’une seule sortie

capable de prendre en entrée une tension entre 40V et 70V : correspond à au moins 2 fois la tension nominale et stresser au minimum le composant et donc de maximiser sa durée de vie

un courant entre 3 et 4 ampères

figure 3 : choix d’un des régulateur à l’aide du site Analog Devices

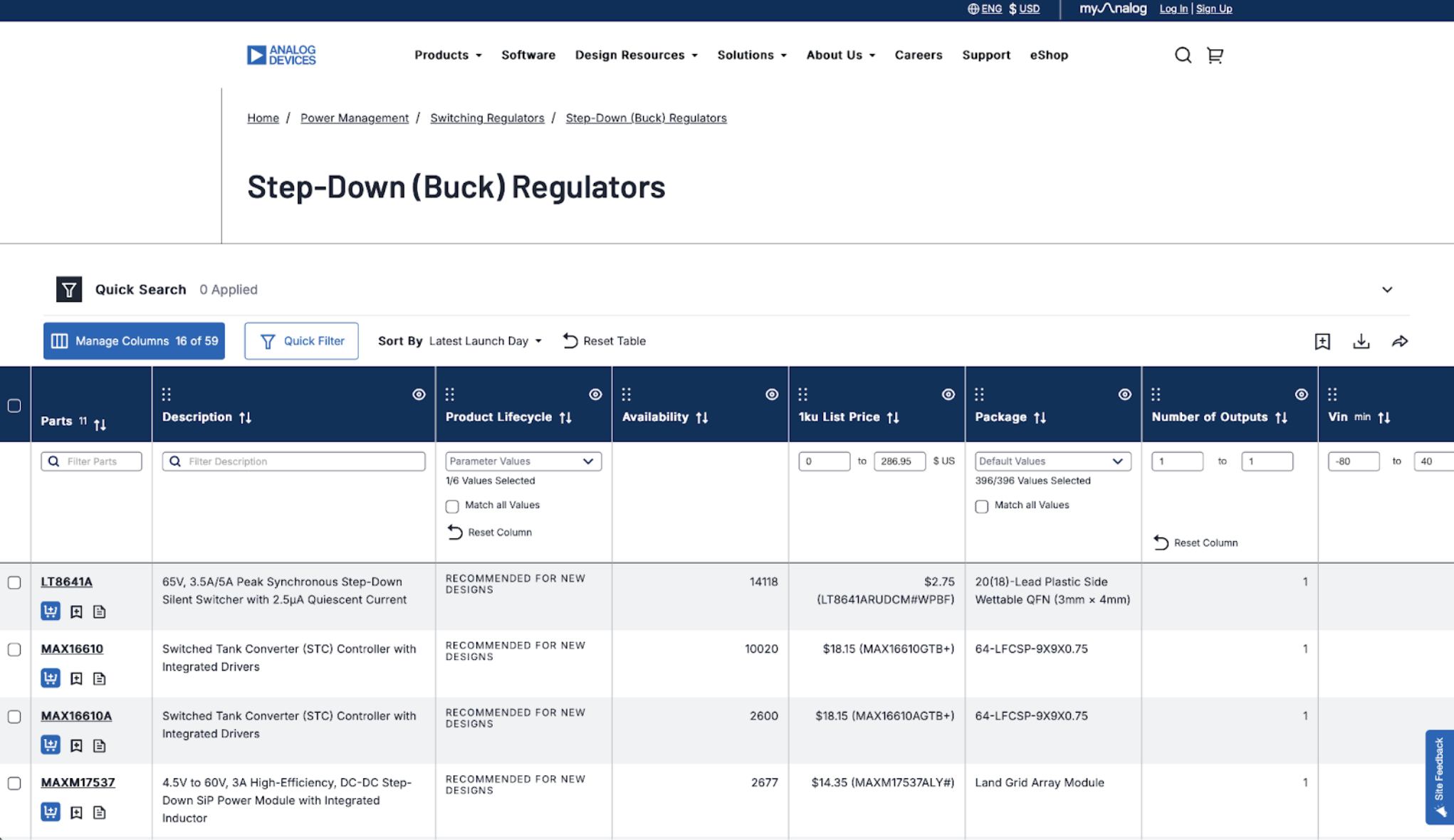

Une fois cette étape répétée pour tous les composants nécessaires, il est important ensuite de dresser un schéma blocs de la partie alimentation ou pourront figurer, la référence des composants choisis, les niveaux de tensions, de courant, les filtres et les résistances de shunt pour la mesure de courant comme le montre la figure 4 ci-dessous:

figure 4 : schéma de blocs de la partie alimentation de la carte DGCTR

J’ai pu réaliser ce schéma à l’aide du logiciel de conception eCADstar schematic editor, qui permet aux ingénieurs de dessiner des schéma électriques, de définir la disposition du PCB et de produire les données de fabrication à partir du PCB terminé.

Conception des étages de régulation

Comme on peut l’apercevoir en figure 1, afin de limiter au maximum le bruit, la régulation de tension se fait en utilisant deux régulateurs. Un premier convertisseur buck (switching regulator), capable d’une chute de tension importante avec un bon rendement mais en générant du bruit, le second, un régulateur linéaire (ultra low noise regulator) très faible bruit.

Le moyen de mise en œuvre et le dimensionnement des régulateurs est disponible dans leur Datasheet, je vais donc utiliser la documentation pour concevoir mon schéma.

Exemple avec la conception d’un régulateur DC/DC 24V vers 5V 1.76A:

La première étape consiste à abaisser la tension de 24V à 5.5V afin de limiter la chute de tension au sein du régulateur linéaire à 0.5V.

Le but de cette étape consiste à dimensionner le pont diviseur R2/R3 afin de fixer la tension de sortie du régulateur LT8641 à 5.5V.

D'après la documentation, la résistance R2 ce calcul ainsi : R2=R3(VOUT0.81-1).

Dans notre cas, nous fixons la valeur de R2 à 1MΩ afin de limiter la consommation de courant par la boucle de rétroaction.

On a donc : R3=R2VOUT0.81-1=1*1065.50.81-1=172,71 kΩ.

Je choisis donc la résistance normalisée la plus proche qui est 162 kΩ. Pour ensuite vérifier mon dimensionnement par simulation avec LTspice :

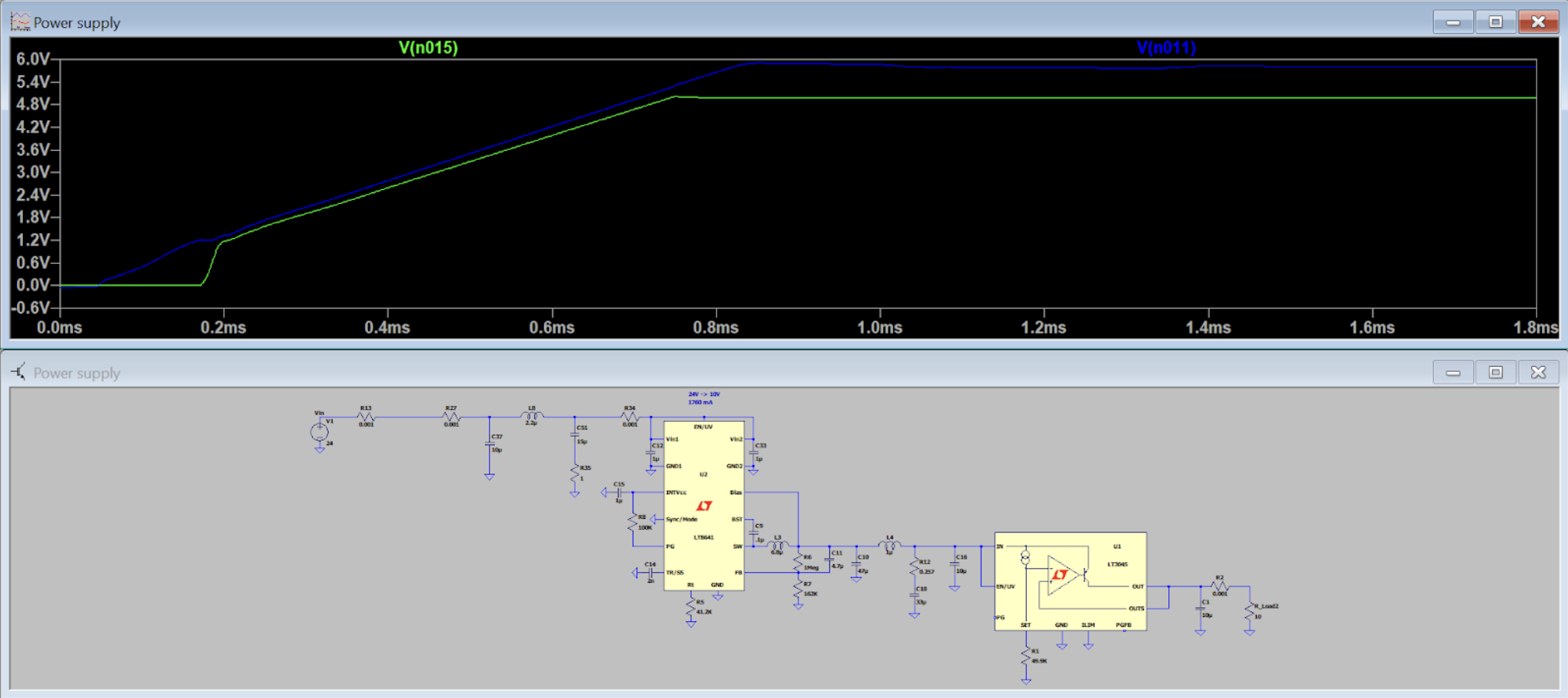

figure 5 : simulation du régulateur BUCK LT8641 avec LTspice

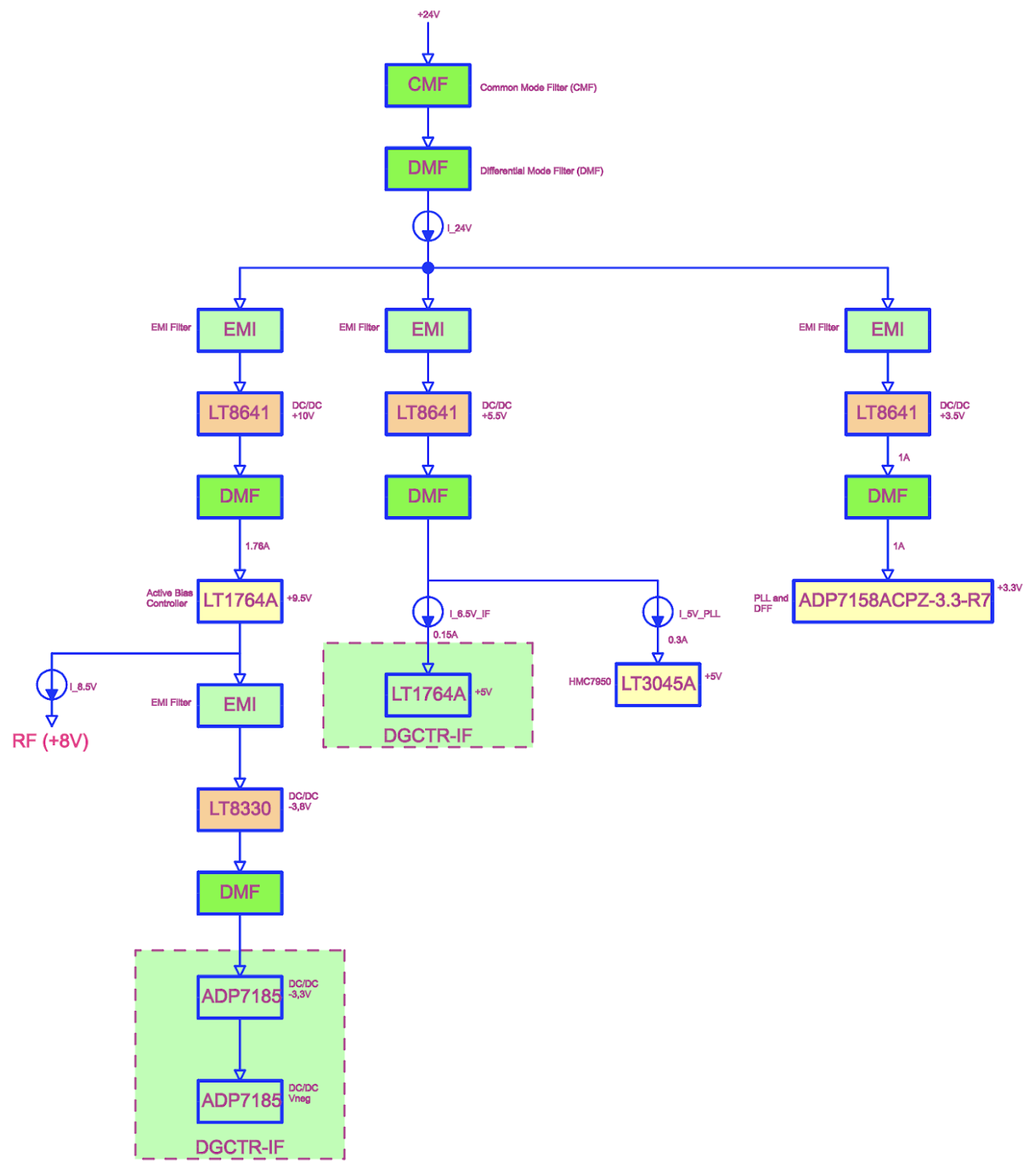

Par la suite, je dois dimensionner le LDO (Low Dropout Regulator) afin qu’il fournisse une tension de 5V en sortie à partir des 5.5V du régulateur BUCK.

D'après la documentation du LT3045, la tension de sortie dépend de deux résistances et est définie par la relation suivante : VOUT=1.21(1+R2R1+3*10-6*R2) comme le montre la figure 6 ci-dessous:

figure 6 : extrait de la Datasheet du LT3045

Je décide donc de choisir une résistance normalisée dont la valeur est de 49.9 kΩ avant de simuler le régulateur seul, puis en série avec le LT8641 comme le montre la figure 7 ci-dessous:

figure 8 : simulation de l’étage d’alimentation complet avec l’entrée du LDO (en bleu) comparée à la sortie (en vert)

Conception des filtres

Le rôle des filtres est d’éviter au maximum de faire remonter du bruit aux composants les plus sensibles comme la PLL et les amplificateurs RF. Ce bruit est dû au type d’architecture des convertisseurs qui utilisent le principe de découpage à l’aide d’un transistor interne. C’est une méthode efficace en termes de rendement et indispensable lorsque la différence de tension entre l’entrée et la sortie est importante (jusqu’à 20V dans notre cas).

La carte comporte deux types de filtres, des filtres EMI, qui sont conçus pour filtrer les hautes fréquences gênantes à l'aide d'un filtre passe-bas ou d’un filtre L-C. Ces filtres sont constitués de composants passifs comme des inductances (L) et des condensateurs (C).

Dans notre cas, le rôle de ce filtre est de supprimer la fréquence de découpage (1MHz) ainsi que les harmoniques induit par le “switching regulator”. Pour ce faire on dimensionne le filtre comme ci-dessous :

On note fsw=1MHz, la fréquence de découpage du régulateur.

La fréquence de résonance est fixée à un dixième de la fréquence de découpage du convertisseur pour atteindre 40dB d’atténuation à la fréquence de découpage,

fc=fsw10=100 KHz

Le régulateur LT8641 nécessite deux condensateurs de 1 µF pour chacune des deux entrées Vin, la valeur du condensateur équivalent d’entrée vaut donc 2µF, noté CIN=2 µF.

La valeur de l’inductance est donnée par la relation suivante :

LF=1(2*pi*fc)2*CIN=1(2*pi*100*103)2*2*10-6=1,2 µH

Pour éliminer la résonance de la cellule LC, un circuit d’amortissement est ajouté en parallèle, composé d’une résistance en série avec une capacité. Les valeurs de R et de C sont calculées à partir des équations suivantes :

Cd=3*CIN=3*2*10-6=6 µF

Rd=2L3*CIN=2*1*10-63*2*10-6=577,4 mΩ

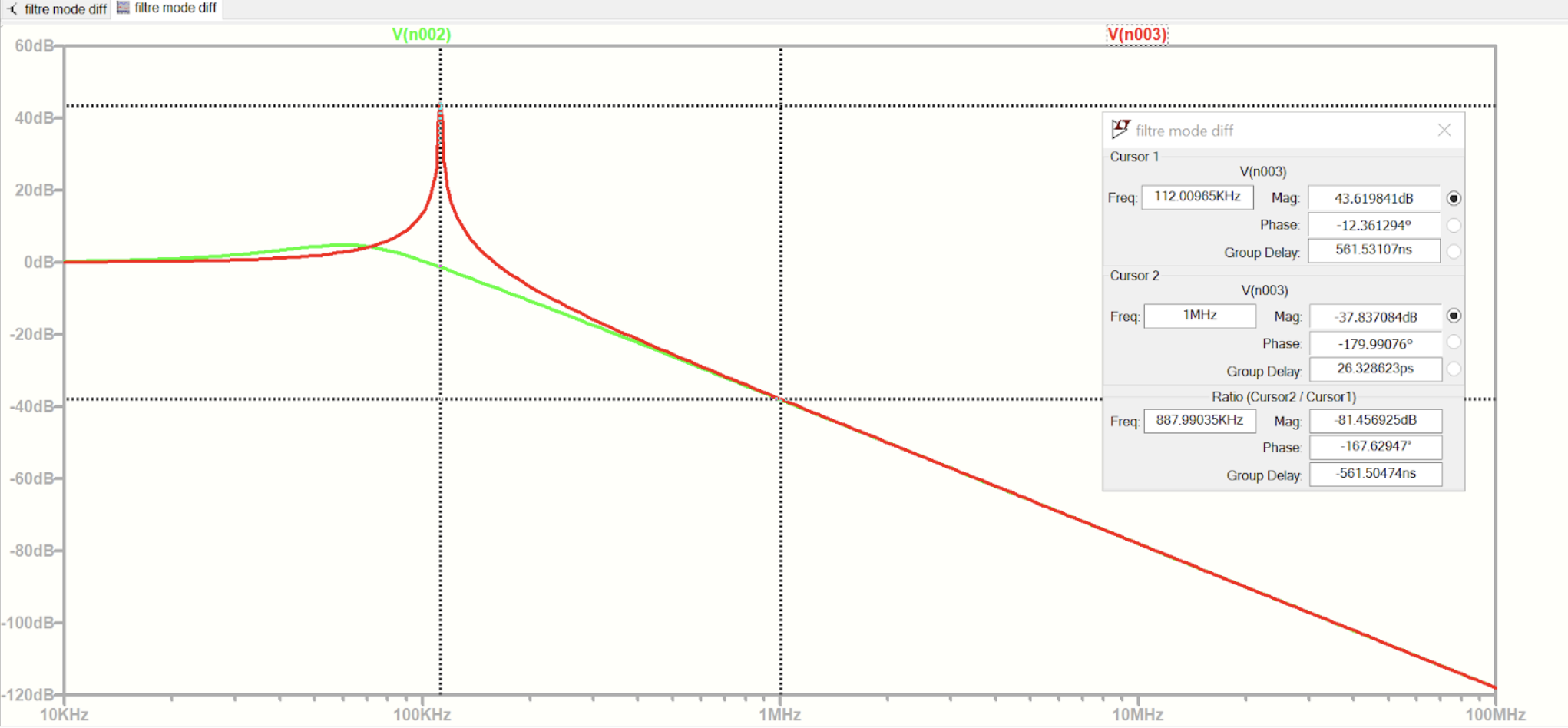

Le filtre une fois dimensionné, je peux donc le simuler à l’aide de LTspice comme le montre la figure 9 ci-dessous:

figure 9 : simulation du filtre seul (sans circuit d’amortissement en rouge, avec en vert)

figure 10 : simulation du filtre appliqué à la sortie du régulateur 8,5V (entrée en vert, sortie en bleu)

Simulation de la carte d'alimentation DGCTR

Cette partie est essentielle car elle permet de valider et dérisquer le fonctionnement des composants ainsi qu’une bonne interaction entre eux.

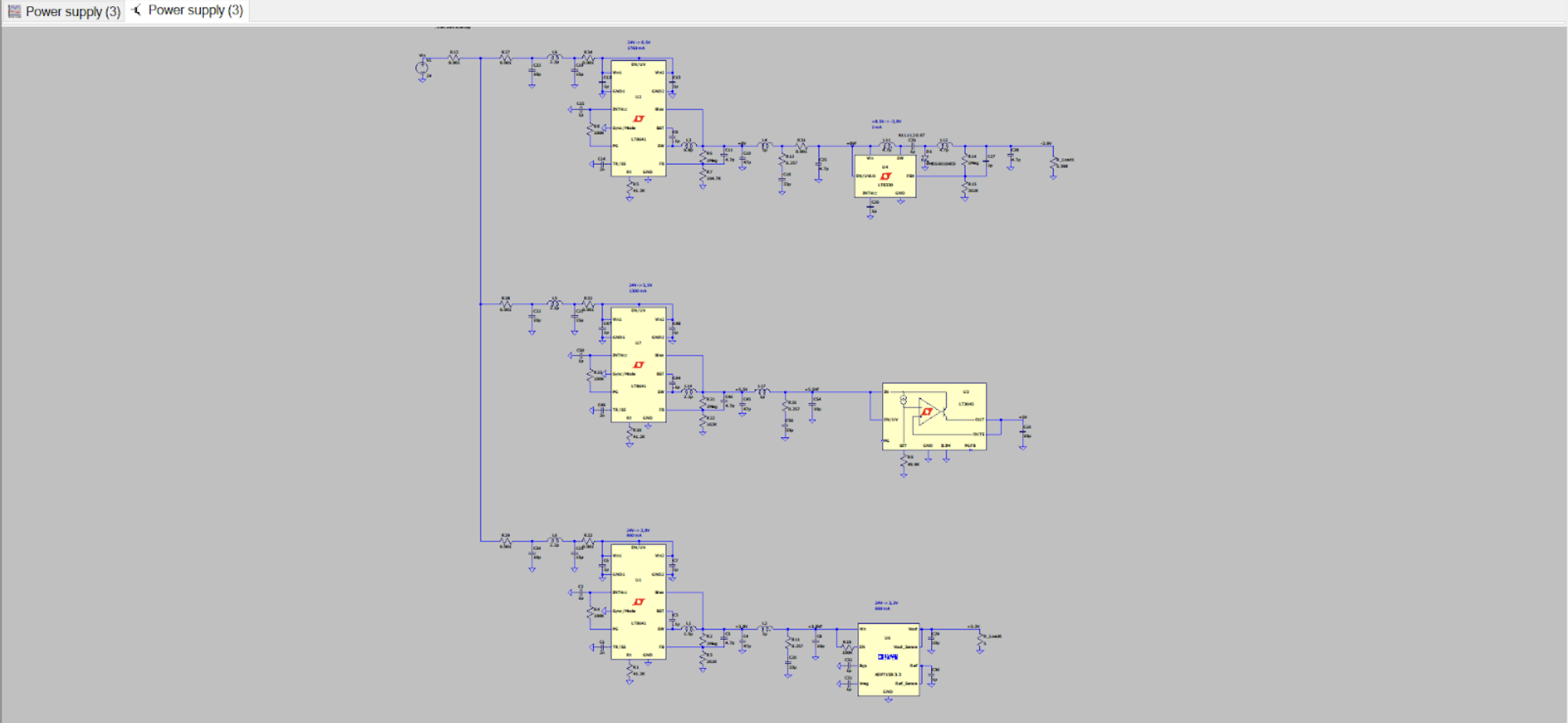

Une fois toutes les parties conçues et simulées, je peux ensuite m’assurer du bon fonctionnement de la partie alimentation complète à l’aide de LTspice comme le montre la figure 11 ci-dessous:

figure 11 : simulation globale de l’alimentation de la carte

La simulation achevée, je peux ensuite effectuer les mesures et les comparer aux mesures des régulateurs seuls afin de m’assurer que leur performance ne se dégrade pas une fois positionnées en série.

Le but de cette vérification est de contrôler si le bruit ne s'additionne pas et si les filtres mis en place sont toujours aussi efficaces.

Conception d’une carte avec eCADstar

Après avoir découvert le logiciel, le fonctionnement est similaire à Cadence, que j’ai déjà utilisé, la transition a donc été assez fluide.

eCADSTAR est un logiciel de conception de circuits imprimés développé par Zuken, combinant un environnement de conception moderne avec des fonctionnalités avancées d’édition et de collaboration cloud.

Il propose un schématicien et un éditeur PCB intégrés, avec des outils de vérification DRC en temps réel, et d'analyse SI/PI pour l'intégrité des signaux et de la puissance. Par rapport à Cadence (Allegro/OrCAD), eCADSTAR offre une interface plus intuitive et connectée au cloud, avec une forte intégration des bibliothèques en ligne et des outils de conception en 3D. Il partage avec Cadence des capacités avancées d’édition de règles, de gestion des empilages multicouches et d'analyse électrique, mais avec une approche plus fluide et automatisée pour la collaboration et la gestion des données.

Importation des composants dans la bibliothèque

Avant toute saisie de schéma il faut logiquement se constituer une bibliothèque de composants qui regroupe pour chaque référence 3 informations majeures : Le symbole, qui apparaît lors de la saisie du schéma ; l'empreinte, qui détermine l’emplacement des pads pour un composant monté en surface ou les trous pour un traversant ; les ouvertures de vernis ainsi qu’une vue 3D et les propriétés qui sont essentielles. C’est ici que nous rentrons les informations concernant le composant comme la référence, le fabricant, la valeur, le fournisseur etc...

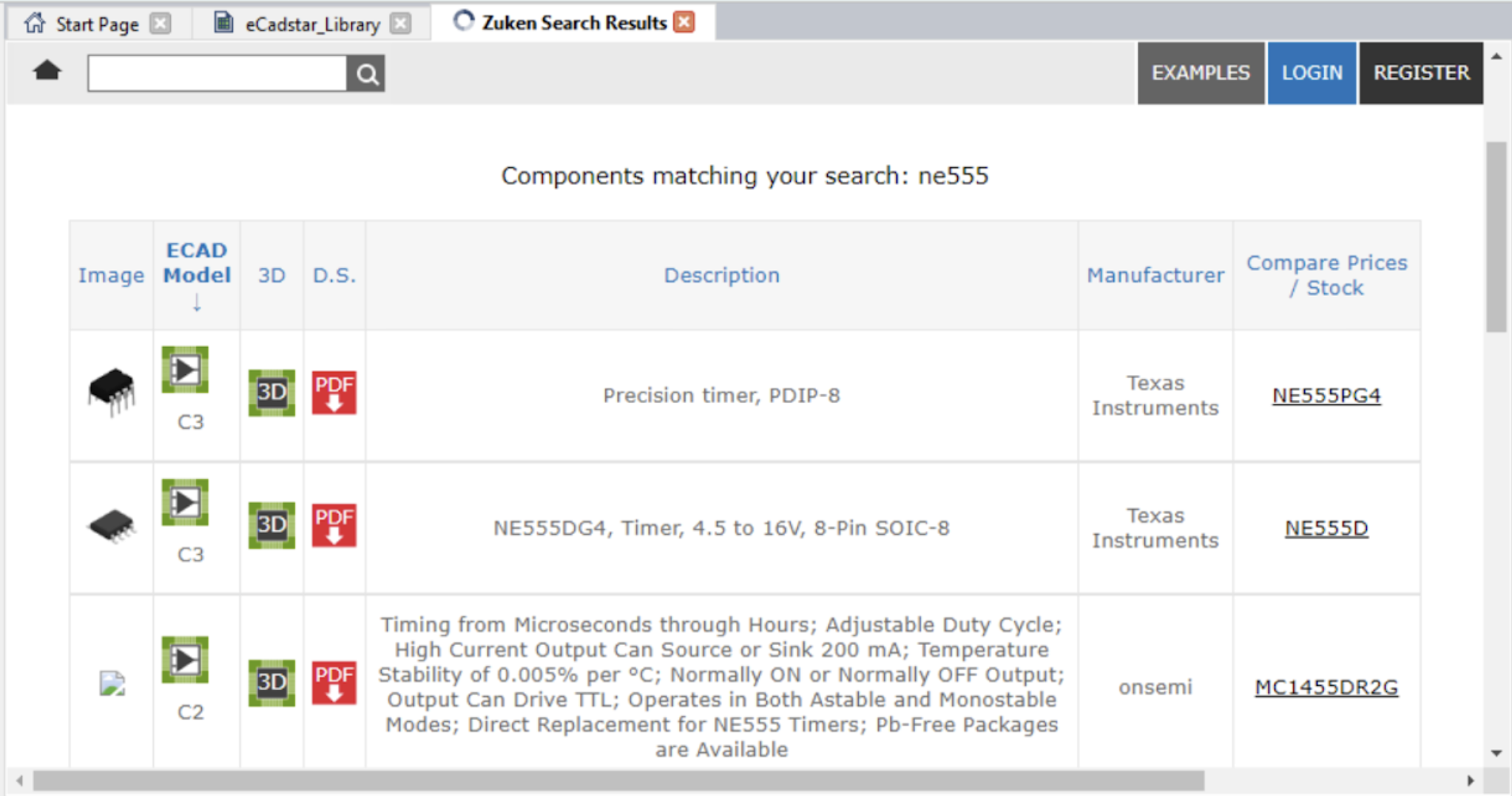

La méthode de l’importation est simple et rapide lorsque le composant a été modélisé par le constructeur ou un membre de la communauté de eCADstar. Il suffit simplement d’ouvrir l'éditeur de librairie “eCADstar library editor”, de se rendre sur l’interface web pour chercher un composant souhaité et le télécharger comme le montre la figure 12 ci-dessous.

figure 12 : exemple de composant (NE555) créé par la communauté

Création d’un composant (symbole, empreinte, propriétés)

Cependant, il se peut que l'empreinte n’ai pas été créé par le fabricant ou par la communauté. Dans ce cas, il faut, à l’aide de la Datasheet, créer le composant à partir de zéro.

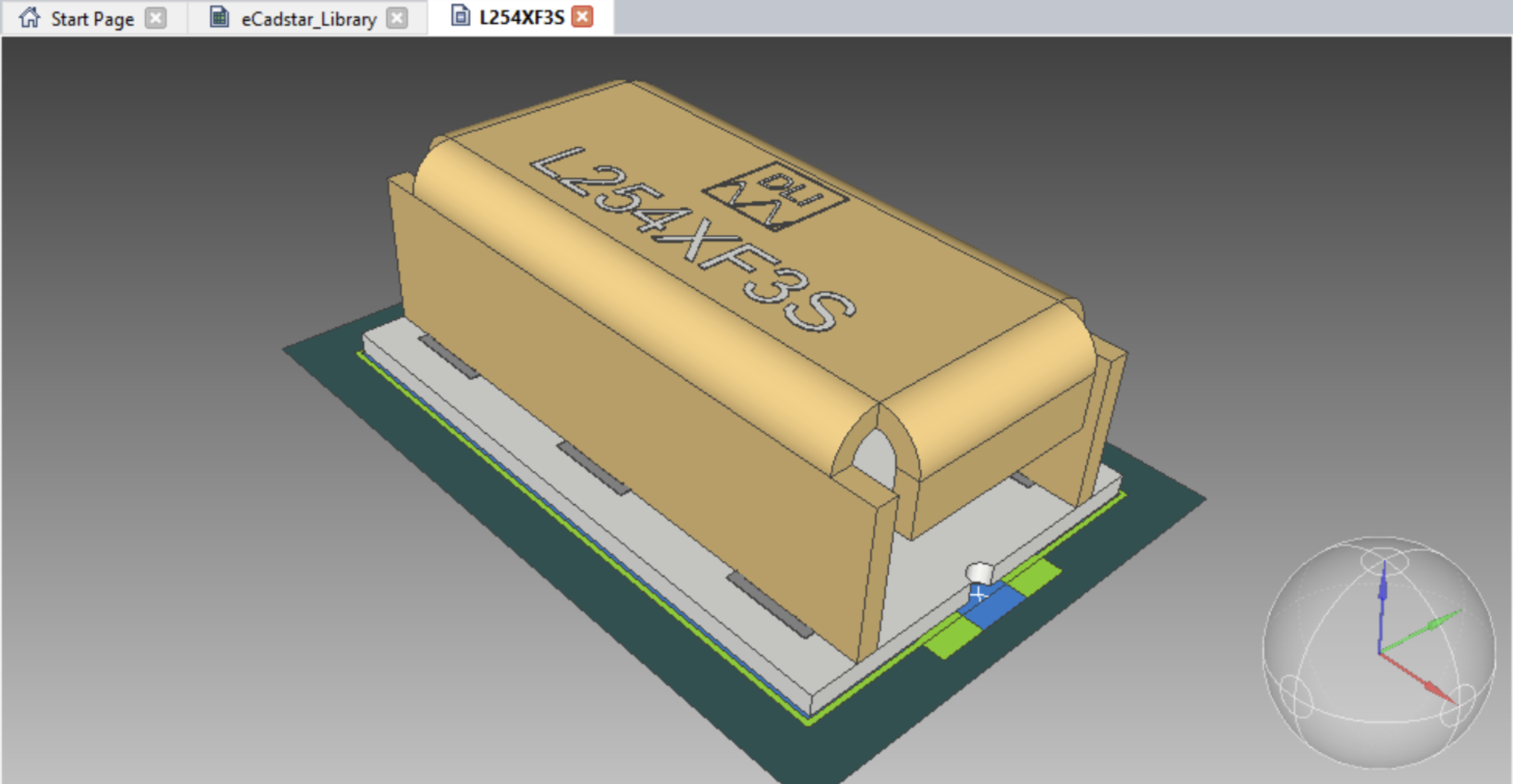

Pour créer le composant à partir de zéro, nous allons donc prendre exemple sur le L254XF3S qui est un filtre passe bas 25,4GHz fabriqué par Knowles Dielectric.

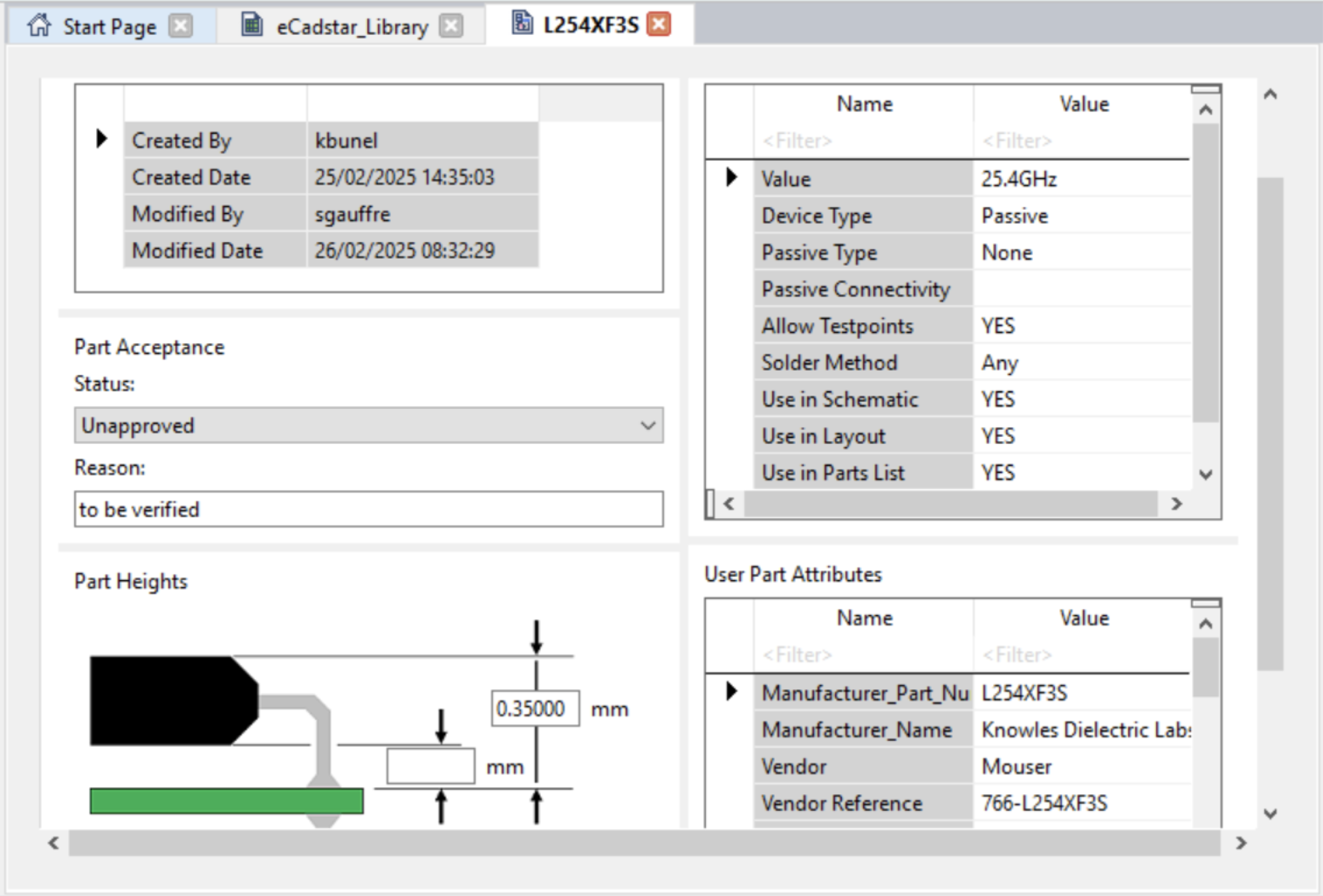

La première étape consiste à créer un nouveau composant dans la librairie et renseigner un maximum d’informations possibles sur le composant dans l’onglet propriétés comme le montre la figure 13 ci-dessous :

figure 13 : propriétés du nouveau composant L254XF3S

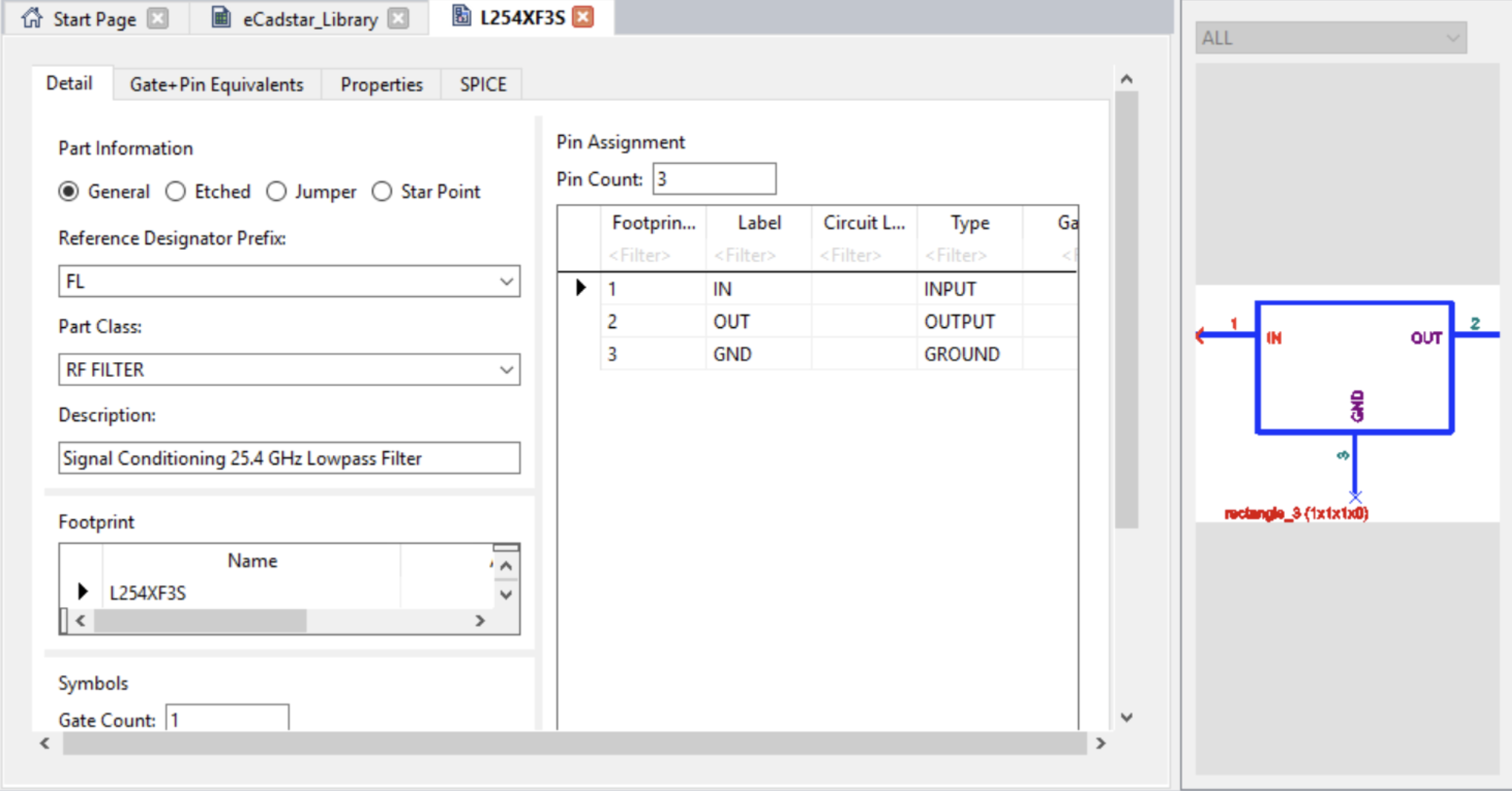

Une fois les propriétés du composant renseignées, il faut ensuite lui assigner un symbole et faire la correspondance avec les broches physiques du composant. Pour cela on utilise un symbole générique qui correspond au mieux au composant comme le montre la figure 14 ci-dessous :

figure 14 : création du symbole du composant et assignation des broches

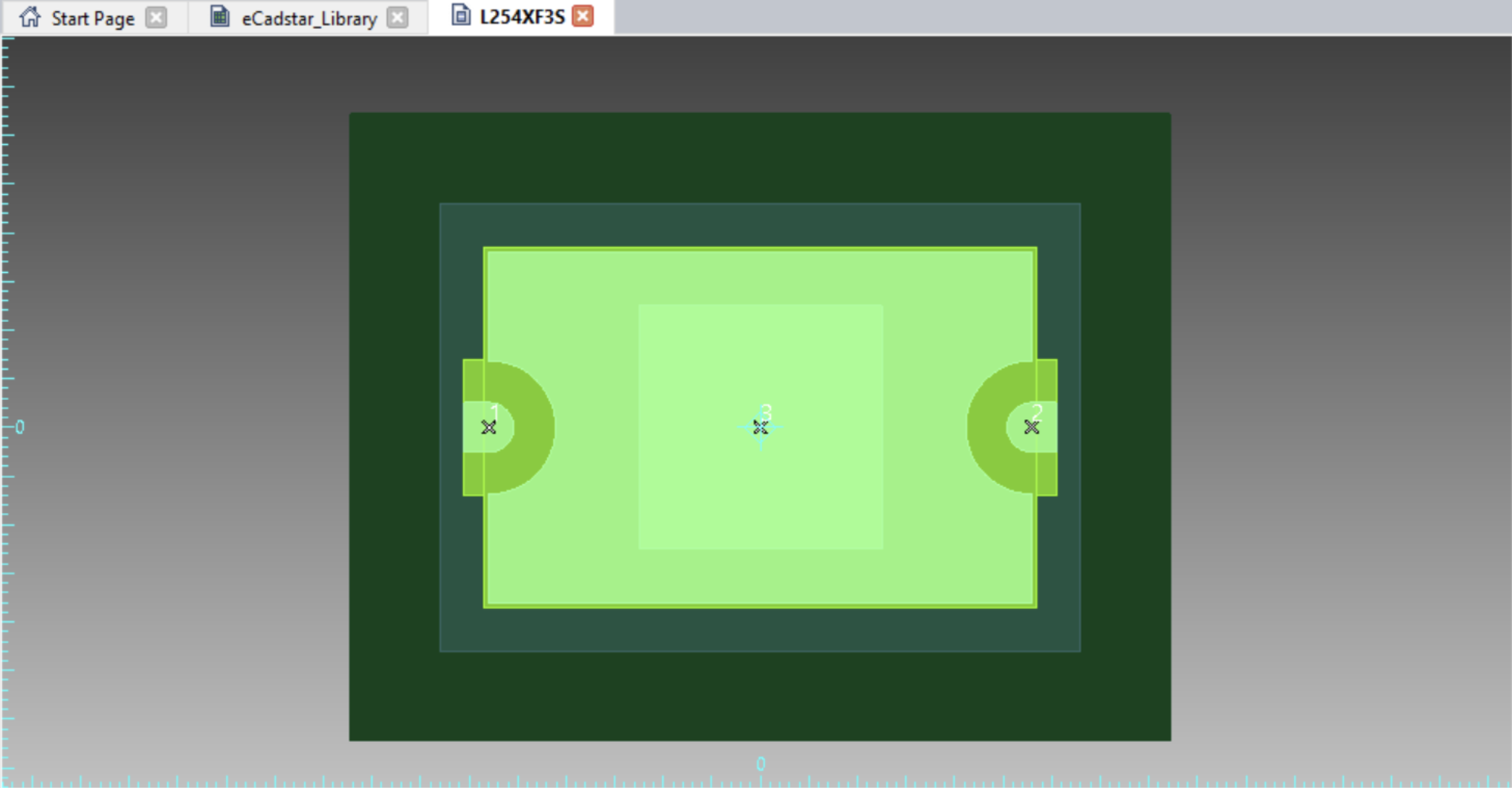

Pour finir, à l’aide de la documentation technique du L254XF3S (disponible en annexe 1), on peut ensuite créer l'empreinte de ce composant comme le montre la figure 15 ci-dessous.

Cette étape est cruciale car impacte directement la possibilité, ou non, de braser le composant sur la carte.

figure 15 : Empreinte du filtre L254XF3S

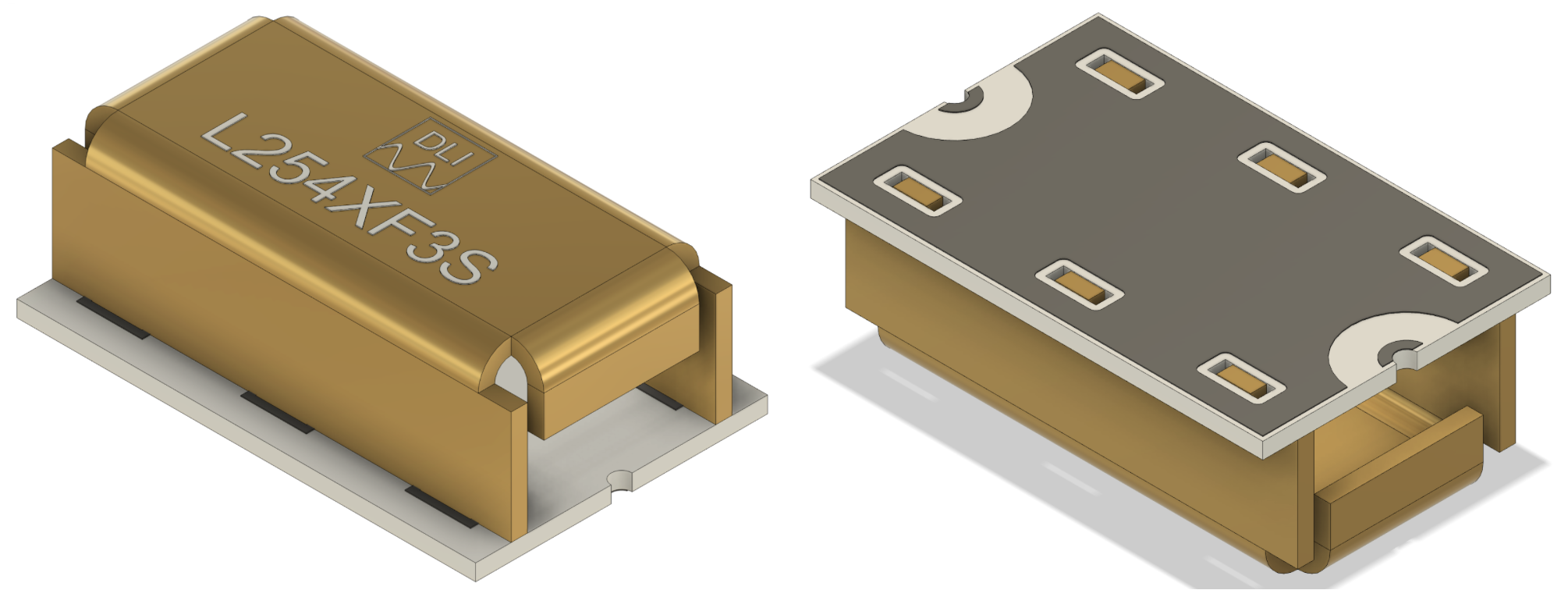

Pour terminer, afin de rendre la conception de la carte la plus fiable possible, il est nécessaire d’importer le modèle 3D du composant. Ce modèle permet de simuler au mieux l’encombrement de la carte.

à l’aide d’un logiciel de conception paramétrique tel que Fusion360 et de la documentation technique (disponible en annexe 1), qui détaille toutes les cotes nécessaire à la réalisation du modèle 3D, il est possible de modéliser le filtre et comme le montre la figure 16 ci-dessous :

figure 16 : modèle 3D du filtre passe bas réalisé

Une fois le modèle 3D réalisé il ensuite l’importer dans eCADstar et l’aligner à l'empreinte comme le montre la figure 17 ci-dessous :

figure 17 : modèle 3D importé et aligné à l'empreinte réalisé plus tôt

Saisi du schéma

Les simulations réalisées et validées, il ensuite possible de saisir le schéma à l’aide de l’outil eCADstar schematic editor afin de saisir le schéma final avec les composants dimensionnés plus tôt en phase de conception.

Pour cette partie la documentation technique des composants devient très utile afin de suivre les notes d’applications. Ces documents permettent une mise en œuvre optimale du composant en proposant des exemples de schémas avec lesquels le composant à été testé et caractérisé afin d’assurer les performances annoncées dans la datasheet.

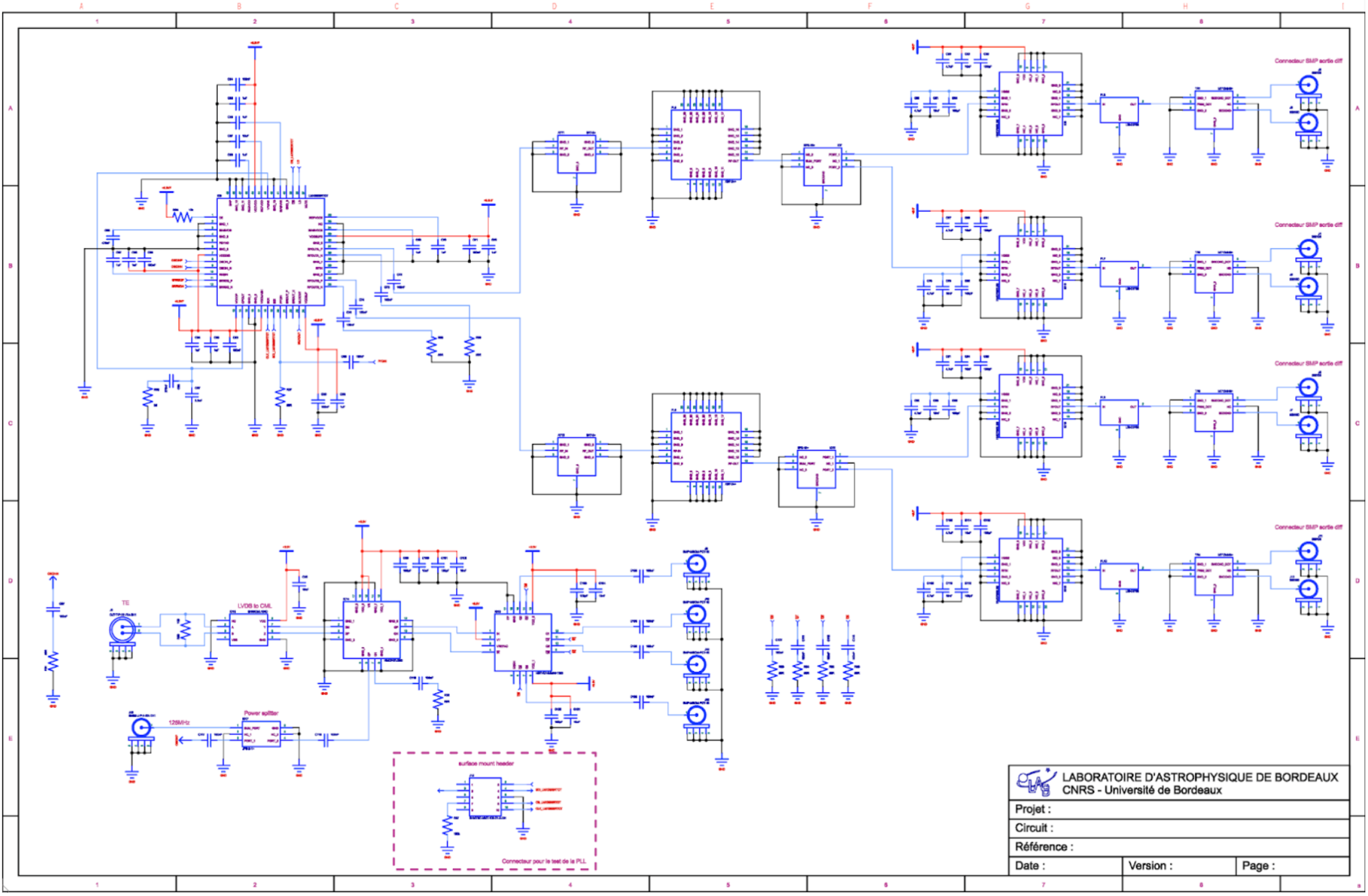

C’est lors de cette étape que j’ai pu découvrir le principe de fonctionnement et la mise en œuvre d’une PLL, en me basant sur un schéma bloc déjà réalisé de la chaîne RF.

Une PLL (Phase-Locked Loop), ou boucle à verrouillage de phase en français, est un système électronique utilisé pour synchroniser la phase et la fréquence d’un signal avec un signal de référence. Utilisée dans notre cas pour multiplier la fréquence d’un signal d’entré, une PLL est un système en boucle fermée composé de trois éléments principaux :

Détecteur de phase (Phase Detector, PD) : Compare la phase du signal d'entrée avec celle du signal généré par l'oscillateur local.

Filtre de boucle (Loop Filter, LF) : Filtre les variations rapides du signal de sortie du détecteur de phase pour obtenir une commande stable.

Oscillateur commandé en tension (Voltage-Controlled Oscillator, VCO) : Génère un signal dont la fréquence est ajustée en fonction du signal d'erreur fourni par le filtre de boucle.

Le principe de la PLL repose sur l'ajustement automatique de la fréquence du VCO pour minimiser la différence de phase avec le signal de référence. Une fois la PLL verrouillée, le VCO suit précisément la fréquence du signal d'entrée.

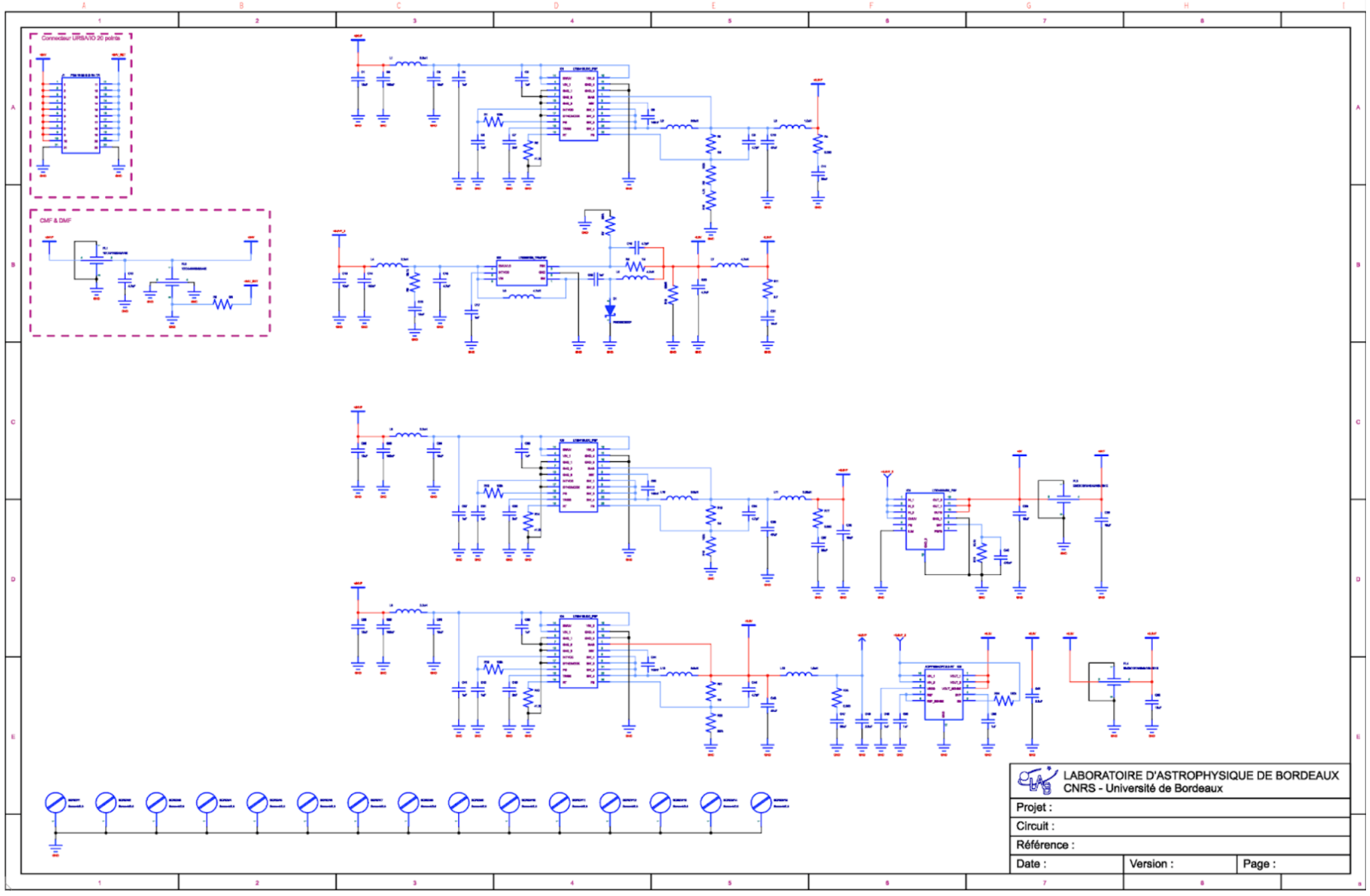

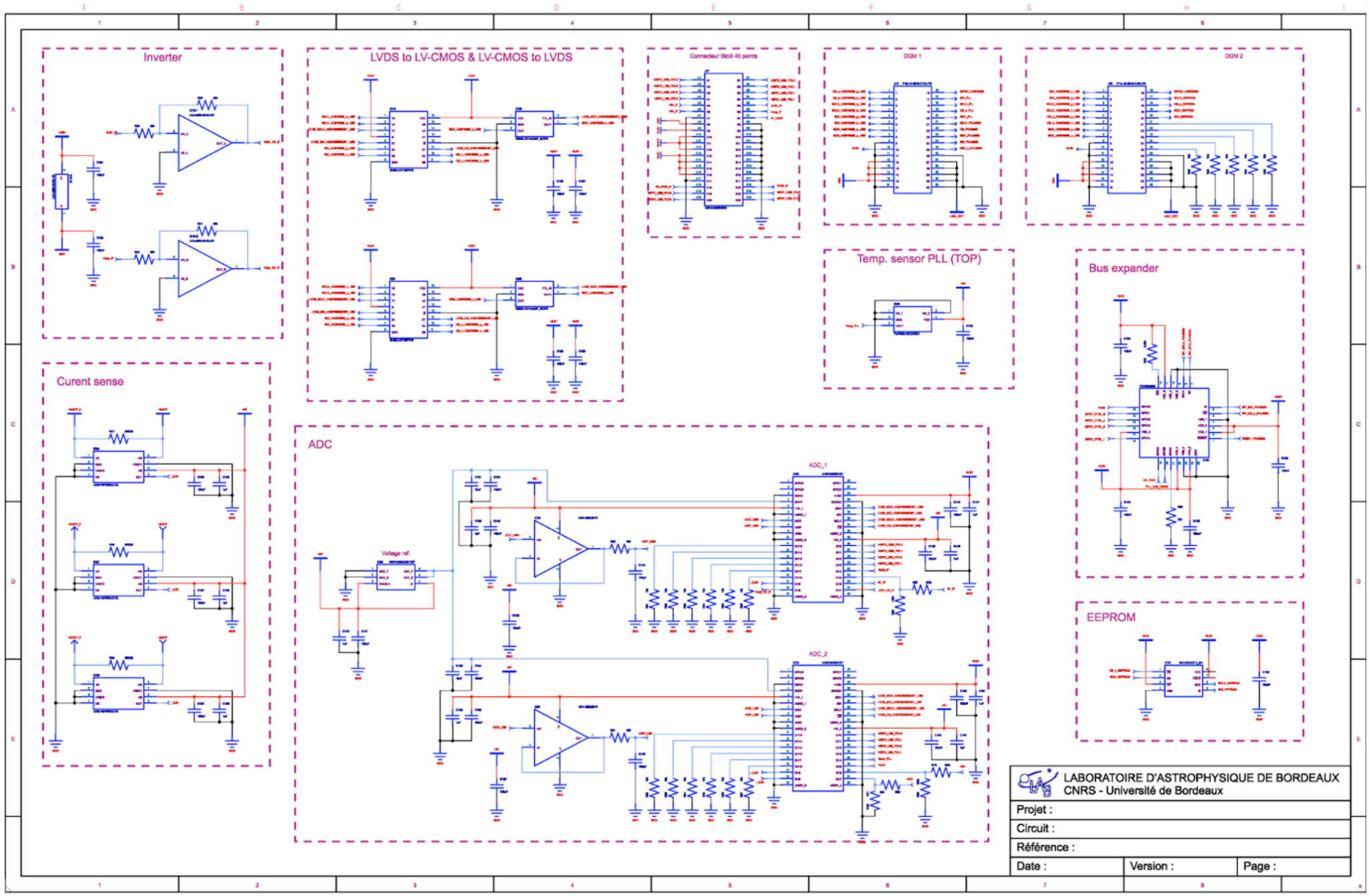

Les schémas réalisés sont disponibles en annexe 2.

Routage de la carte

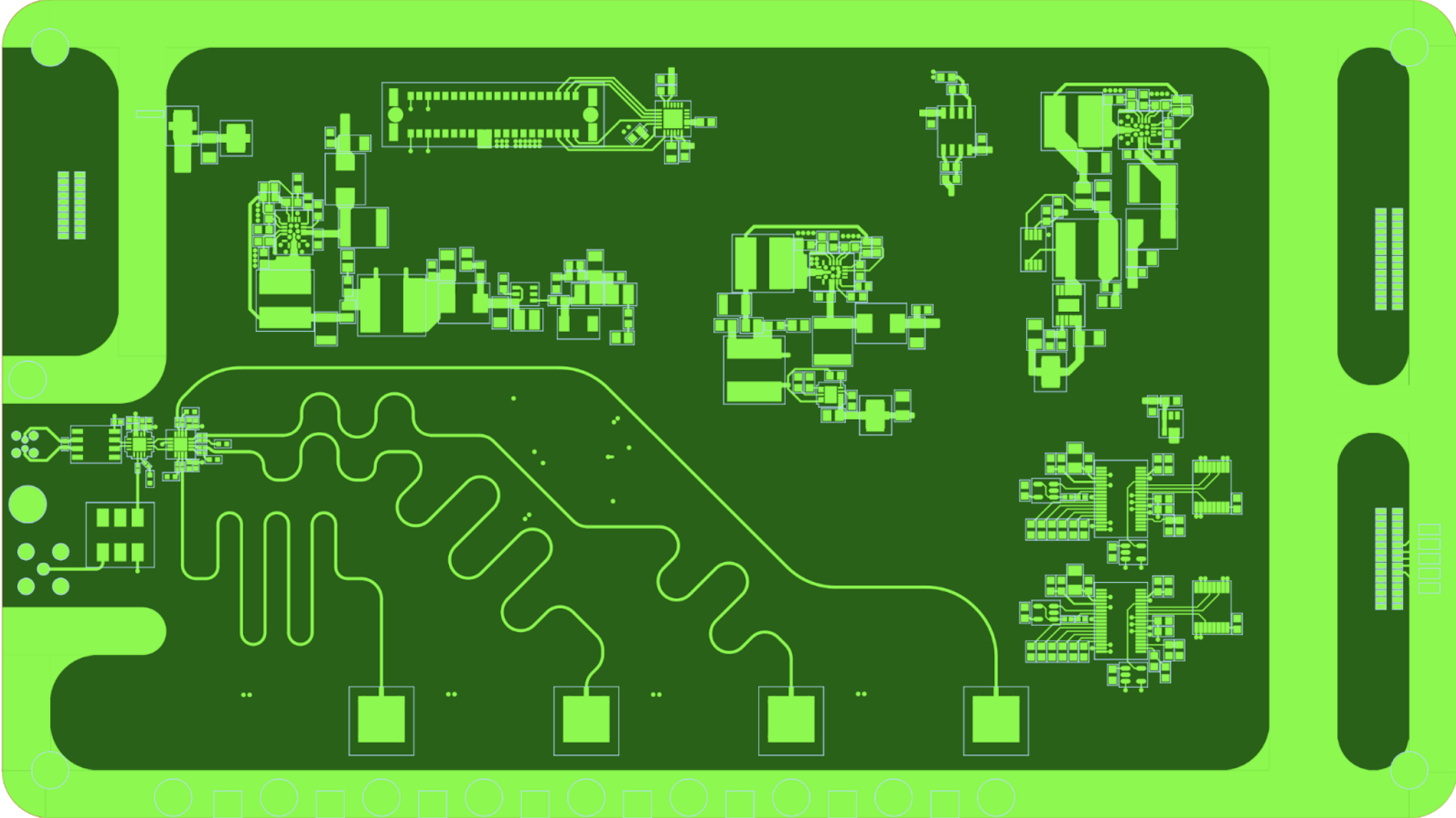

Le routage d’une carte électronique à 6 couches est une étape cruciale qui permet d’optimiser la distribution des signaux, de l’alimentation et de la masse tout en réduisant les interférences électromagnétiques (EMI) ce qui est essentiel dans mon cas.

Lors de la conception, il est essentiel de respecter les normes IPC (Institute for Printed Circuits) qui ont les règles générales de conception et les exigences de fabrication. Ces normes garantissent la fiabilité, la fabricabilité et la conformité aux exigences industrielles, assurant ainsi une production efficace et des performances optimales de la carte.

Dans mon cas les couches de la cartes sont dédiées ainsi :

La couche TOP (1) comporte la partie alimentation (convertisseurs DC-DC), la partie numérique (ADC, translateurs de niveaux) et la distribution du signal de référence.

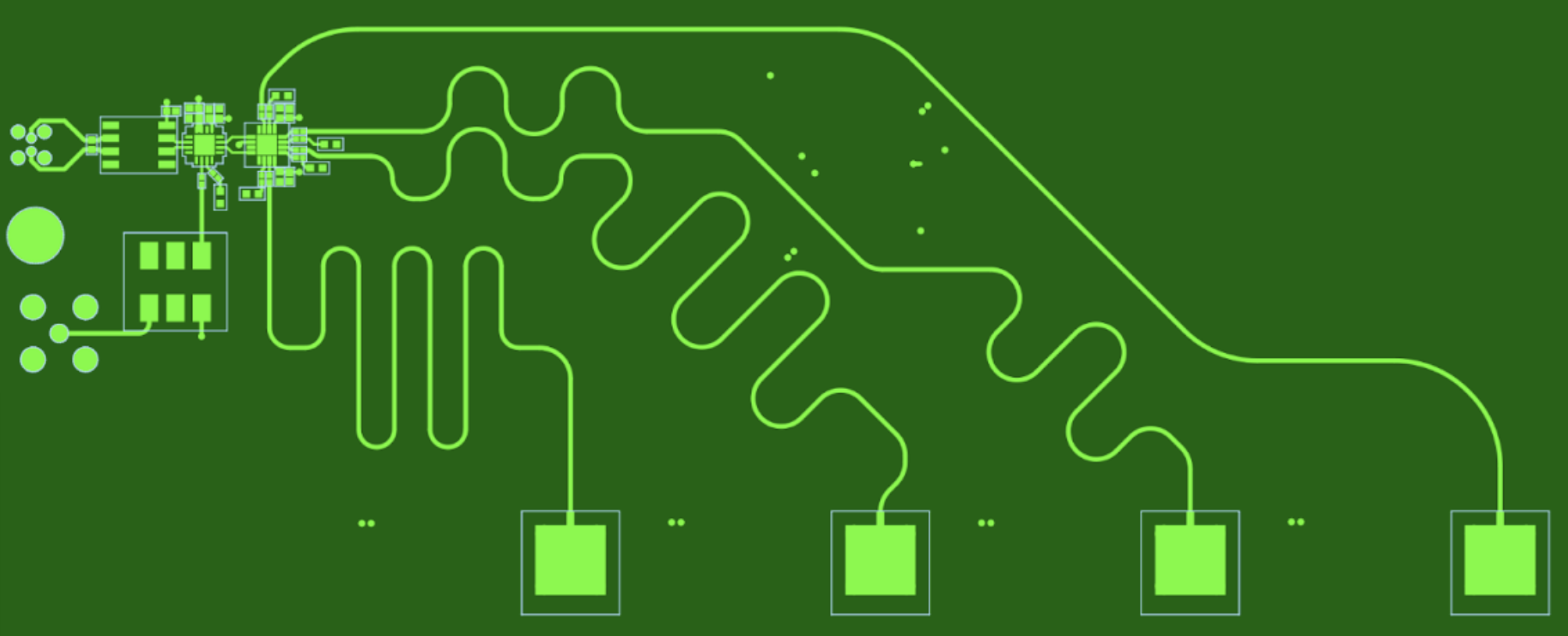

La synchronisation de ses signaux étant également un point clé, il faut donc prendre en compte la propagation du signal dans les pistes qui distribuent les signaux vers les connecteurs en s'assurant qu’elles soient de la même longueur, pour atteindre une précision de l’ordre de la période d’échantillonnage. Pour cela je route les signaux et mesure la piste la plus longue, ensuite j'utilise une fonction du logiciel eCADstar pour rallonger les autres pistes afin de faire correspondre les longueurs comme le montre la figure 18 ci-dessous :

figure 18 : compensation des longueurs de pistes

Un anneau de garde à été placé tout le tour de la carte, cette anneau à pour but de minimiser le bruit au sein de la carte et prend la forme d’une ouverture de vernis tout le tour de celle-ci afin qu’un châssis métallique soit en contact avec le plan de masse comme le montre le routage final de la couche TOP de la carte ci-dessous :

figure 19 : routage final de la couche 1 (TOP)

La couche 3 est dédiée aux signaux numériques SPI qui concernent les DAC et la PLL qui utilisent ce protocole pour communiquer et modifier leurs paramètres.

La couche 4 et le plan d’alimentation, c’est ici que sera distribué les tensions nécessaires à travers toute la carte pour alimenter les composants.

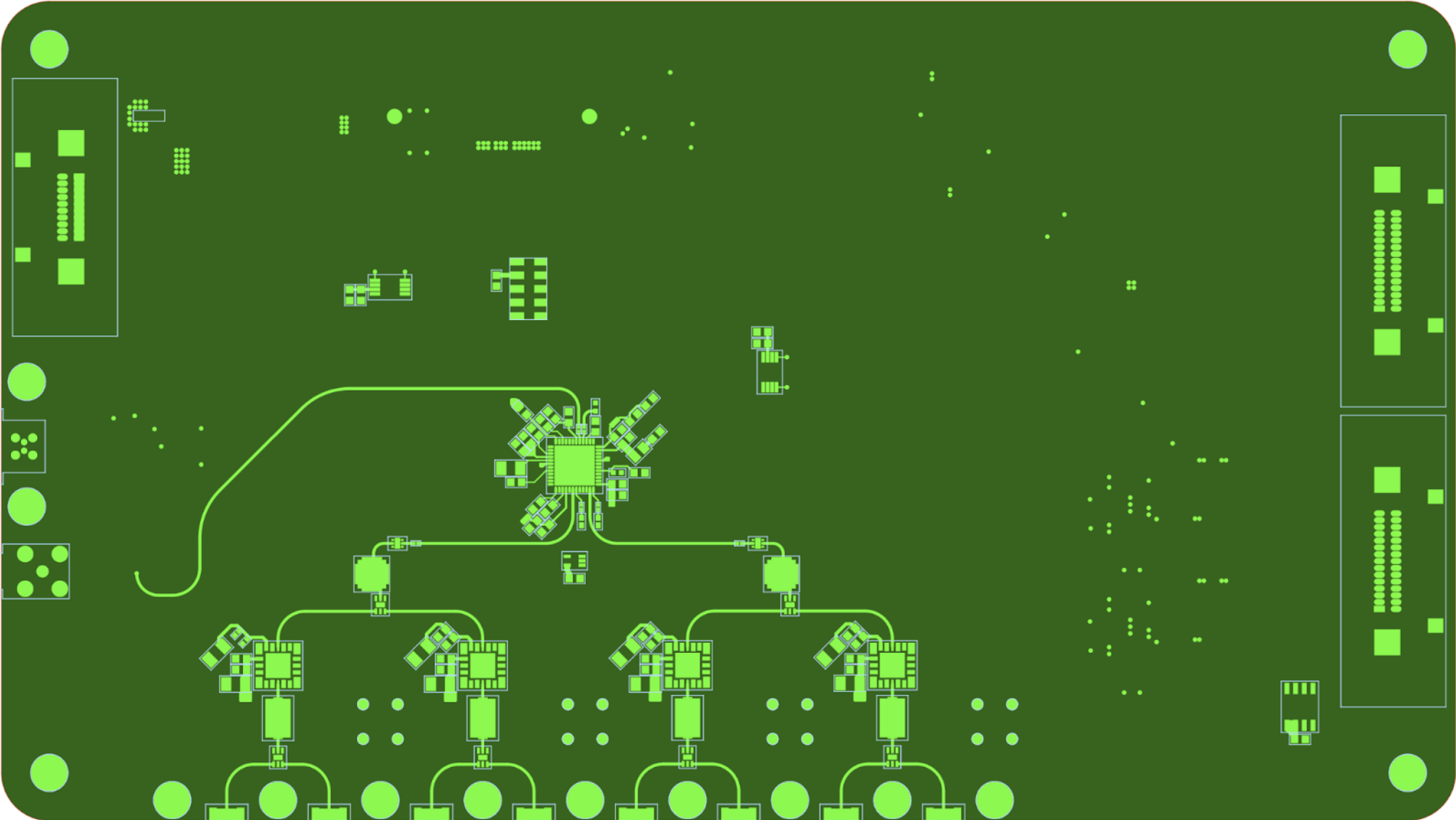

La couche BOTTOM (6) accueille la partie haute fréquence qui comporte la PLL ainsi que les filtres et amplificateurs haute fréquence. Cette partie nécessite une attention toute particulière car sensible au bruit et a un impact direct sur les performances de la carte.

Sachant que les signaux de sortie de la PLL sont en différentiel, il est donc primordial de réaliser un routage le plus symétrique possible.

Pour ce faire je peux m’aider de deux fonctionnalités de eCADstar ; les coordonnées, très utile pour positionner les composants à une distance connue les uns de autres et l’outil “copy placement” qui permet de dupliquer un routage afin de placer les composants exactement au même emplacement. comme le montre la figure 20 ci-dessous :

figure 20 : routage de la couche BOTTOM de la carte (PLL + chaîne RF)

Les couches 2 et 5 sont des plans de masses afin de limiter au maximum la pollution des signaux de la partie RF et PLL

Conclusions

En conclusion, les règles de conception IPC jouent un rôle crucial dans le développement d’une carte électronique.

Elles garantissent la fiabilité, la fabricabilité et la performance du circuit tout en réduisant les risques d’interférences électromagnétiques, d’atténuation du signal et de défauts de fabrication.

En suivant ces normes, les concepteurs assurent une meilleure compatibilité avec les procédés de production et d’assemblage et optimisent le rendement et la durée de vie du produit.

Du point de vue personnel, j’ai trouvé mon expérience de stage au sein du laboratoire d'astrophysique de Bordeaux, extrêmement enrichissante.

L'implication de mes tuteurs, formateurs et autres ingénieurs et techniciens du laboratoire, m’ont permis de développer plusieurs de mes compétences abordées en cours, comme la conception d’une carte haute fréquence, allant du dimensionnement, à la lecture de datasheet, de notes d'application en passant par la réalisation d’un schéma et finir par le routage.

J'ai de même pu découvrir de nouveaux outils et logiciels et ainsi acquérir de nouvelles compétences d’utilisation sur eCADstar Library editor, schematic editor ou encore PCB editor.

Par la même occasion j’ai pu renforcer mes connaissances de conception 3D sur Fusion 360.

Ce stage a permis d'appréhender ma capacité à m’intégrer au sein d’un projet complexe, de grande ampleur et en cours depuis plusieurs années, de m’adapter, de trouver ma place au sein d’une équipe et pouvoir ainsi, participer, activement au projet commun.

Le personnel en place, ouvert à la transmission de leurs connaissances, passionné par leur métier, m’a permis d’aborder tous les sujets, les questionnements et me sentir totalement impliqué au sein du laboratoire.

Kyrian BUNEL

Annexes

Annexe 1 : extrait de la Datasheet du L254XF3S montrant ses caractéristiques mécaniques et le layout recommandé par la fabricant

Annexe 2 : schémas réalisés de la carte DGCTR PLL

feuille 1 : partie alimentation et filtrage

feuille 2 : partie PLL et haute fréquence avec distribution du TE

feuille 3 : partie numérique, ADC, EEPROM, mesures de courant

Annexe 3 : Rendu 3D final de la carte